## F-HEE-DIO-LVTTL-16IO

## **HotRIO Eurocard Expansion board**

- 16 LVTTL channels with copper interfaces

- Two banks of 8 channels, each bank independently configurable as input or output

- Supports LVTTL voltage levels for both input and output

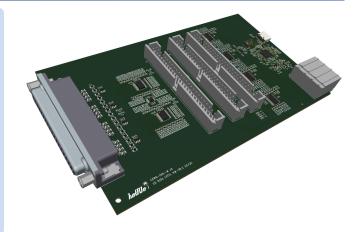

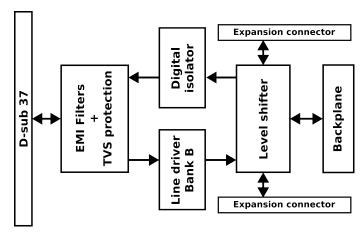

Functionally, the F-HEE-DIO-LVTTL-16IO serves as a robust, transparent digital interface between the field-side DB-37 connector and the system backplane. Signals from the controller board's FPGA enter via the backplane connector and are first conditioned by voltage level shifters (converting 1.8 V logic to 3.3 V LVTTL), followed by line buffers and drivers equipped with Schmitt triggers. This arrangement ensures clean, reliable signal transitions and high noise immunity.

All sixteen channels adhere to the LVTTL voltage standard, supporting low-voltage, high-speed digital signaling. The board's architecture provides full electrical isolation between the backplane and the field wiring, significantly enhancing system safety and reducing susceptibility to electrical noise.

No onboard data processing occurs; instead, the board faithfully transmits signals between the controller and external devices, making it ideal for applications demanding flexible, isolated digital I/O with configurable directionality.

## **Technical Specifications**

| Form factor            | 100x160 mm (Eurocard)      |

|------------------------|----------------------------|

| Mounting               | Eurocard chassis           |

| Backplane interface    | HotRIO Type A              |

| Digital channels       | 16 (LVTTL, fully isolated, |

|                        | configurable in 2 banks of |

|                        | 8 as input or output)      |

| Isolation method       | Line drivers               |

| Input/output connector | DB-37 (front panel)        |

| Power supply           | 5V DC (from backplane)     |

| Power consumption      | TBD W                      |

**Warning:** This document exclusively describes the hardware detailed herein. Any reference to software or firmware used to operate this hardware is outside the scope of this document.

Developers are advised to consult separate documentation for any information related to software or firmware functionality.

## 1 License

Copyright 2024 F4E — European Joint Undertaking for ITER and the Development of Fusion Energy ('Fusion for Energy').

This source describes Open Hardware and is licensed under the CERN-OHL-W v2 You may redistribute and modify this documentation and make products using it under the terms of the CERN-OHL-W v2.

This documentation is distributed WITHOUT ANY EXPRESS OR IMPLIED WARRANTY, INCLUDING OF MERCHANTABILITY, SATISFACTORY QUALITY AND FITNESS FOR A PARTICULAR PURPOSE.

As per CERN-OHL-W v2 section 4.1, should You produce hardware based on these sources, You must maintain the Source Location visible on the external case of the product you make using this documentation.