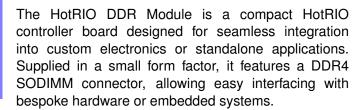

## F-HSC-DDR

## **HotRIO Standalone Controller board**

- Compact form factor for custom applications.

- Recommended solution to embed HotRIOprotocol into custom designs.

- Standard DDR4 connector interface the FPGA.

- Two individual SFP interfaces.

At its core, the board is built around a Lattice ECP5 LFE5UM5G-85F FPGA, complemented by a dedicated manager microcontroller for board management and configuration. Two SFP ports provide high-speed optical or copper connectivity, enabling the board to operate as either a master or slave on a HotRIO bus, as well as supporting UDP communication.

This board is functionally analogous to the F-HEC-PIR board (codename Piranha), but is specifically tailored for embedded applications where space is limited or where HotRIO capabilities must be added to an existing system without the need for a bulky Eurocard chassis. The HotRIO DDR Module exposes all LVDS pair outputs (both clock-capable and regular pairs) and several LVTTL pins via the DDR connector, making it ideal for hardware developers seeking a flexible and compact HotRIO solution.

By leveraging the DDR4 SODIMM connector, the HotRIO DDR Module enables straightforward integration of custom hardware into the HotRIO ecosystem. Designers can develop bespoke carrier boards or daughtercards that interface directly with the module's high-speed LVDS pairs and LVTTL signals, allowing for rapid prototyping and deployment of application-specific solutions.

## **Technical Specifications**

| Form factor              | 66 x 73 mm                                                      |

|--------------------------|-----------------------------------------------------------------|

| FPGA                     | LFE5UM5G-85F                                                    |

| Interface connector      | SO-DIMM DDR4                                                    |

| FPGA interfaces          | 64 x LVDS pairs,                                                |

| Communication interfaces | 2 x SFP modules (up to 1 Gbps each)                             |

| Clock inputs             | 50 MHz internal oscillator,<br>10 MHz external clock via<br>SMB |

| Time sync                | 1 x external PPS signal via SMB                                 |

| Power supply             | 5 V DC through USB or<br>SO-DIMM DDR4 connec-<br>tor            |

Within a HotRIO system, the DDR Module can function as either a master or slave node. As a master, it allows developers to control and communicate with a network of HotRIO-capable devices, integrating remote I/O seamlessly into their system. Alternatively, when configured as a slave, the board acts as a data provider to an existing HotRIO infrastructure.

This flexibility enables developers to embed custom electronics into the HotRIO ecosystem—either as data producers or as gateways for HotRIO protocol integration. For example, if an existing electronic system requires direct access to multiple HotRIO devices, the DDR Module can be interfaced via a standard SO-DIMM connector, much like a network interface card (NIC). This approach allows rapid expansion of system capabilities, providing straightforward connectivity to HotRIO devices without the need for bulky hardware or complex integration steps.

**Warning:** This document exclusively describes the hardware detailed herein. Any reference to software or firmware used to operate this hardware is outside the scope of this document.

Developers are advised to consult separate documentation for any information related to software or firmware functionality.

## 1 License

Copyright 2024 F4E — European Joint Undertaking for ITER and the Development of Fusion Energy ('Fusion for Energy').

This source describes Open Hardware and is licensed under the CERN-OHL-W v2 You may redistribute and modify this documentation and make products using it under the terms of the CERN-OHL-W v2.

This documentation is distributed WITHOUT ANY EXPRESS OR IMPLIED WARRANTY, INCLUDING OF MERCHANTABILITY, SATISFACTORY QUALITY AND FITNESS FOR A PARTICULAR PURPOSE.

As per CERN-OHL-W v2 section 4.1, should You produce hardware based on these sources, You must maintain the Source Location visible on the external case of the product you make using this documentation.