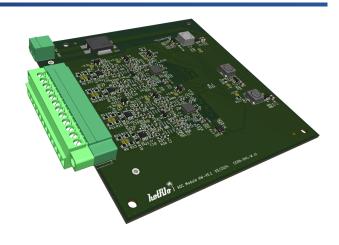

## F-HSE-ADC-DDR

## **HotRIO Standalone Expansion board**

- Four independent 20-bit ADC channels, each supporting up to 2 MHz sampling rate

- Direct interface to HotRIO F-HSC-DDR controller board

- Standalone operation without additional infrastructure

- High-precision analog-to-digital conversion for demanding applications

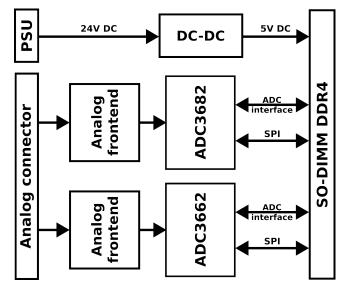

The HotRIO F-HSE-ADC-DDR is a standalone expansion board with two ADC ICs, each providing two independent channels. Each channel supports sampling rates up to 2 MHz at 20-bit resolution.

The board is designed for integration with the HotRIO F-HSC-DDR standalone controller for analog-to-digital conversion. This solution is ideal for use-cases where standalone ADCs must be provided without any other equipment, allowing deployment of a single HotRIO-compliant node with the ADCs, without the need for additional infrastructure such as a Eurocard chassis.

The F-HSE-ADC-DDR board is intended for applications where analog signals must be digitized in close proximity to their source, such as in remote or distributed environments. In scenarios where sensors are deployed in the field, this board enables local analog-to-digital conversion, thereby minimizing the need for extended analog cabling, which can be prone to noise and signal degradation. By performing digitization at the source, only digital data needs to be transmitted, significantly reducing susceptibility to interference.

Unlike the full HotRIO eurocard chassis, which is large and includes a wide range of I/O options, this board is compact and focused. It provides the essential HotRIO functionality for ADC applications without the bulk and complexity of the full chassis, making it ideal for installations where space is limited and only ADC capability is required.

## **Technical Specifications**

| Form factor         | 100 x 100 mm                                                           |

|---------------------|------------------------------------------------------------------------|

| Interface connector | SO-DIMM DDR4                                                           |

| ADCs                | 1x ADC3662, 1x ADC3682                                                 |

| Number of channels  | 4 (2 per ADC)                                                          |

| Sampling rate       | Up to 2 MHz per channel                                                |

| Resolution          | Up to 16-bit (ADC3662),<br>up to 20-bit with decima-<br>tion (ADC3682) |

| Filters             | Digital decimation and FIR filters (ADC3682)                           |

| ADC input voltage   | ±1.6 V                                                                 |

| ADC connector       | Phoenix Contact MC 1,5/12-GF-3,5                                       |

| Power supply        | 24 V DC connector or 5 V DC via SO-DIMM connector                      |

**Warning:** This document exclusively describes the hardware detailed herein. Any reference to software or firmware used to operate this hardware is outside the scope of this document.

Developers are advised to consult separate documentation for any information related to software or firmware functionality.

## 1 License

Copyright 2024 F4E — European Joint Undertaking for ITER and the Development of Fusion Energy ('Fusion for Energy').

This source describes Open Hardware and is licensed under the CERN-OHL-W v2 You may redistribute and modify this documentation and make products using it under the terms of the CERN-OHL-W v2.

This documentation is distributed WITHOUT ANY EXPRESS OR IMPLIED WARRANTY, INCLUDING OF MERCHANTABILITY, SATISFACTORY QUALITY AND FITNESS FOR A PARTICULAR PURPOSE.

As per CERN-OHL-W v2 section 4.1, should You produce hardware based on these sources, You must maintain the Source Location visible on the external case of the product you make using this documentation.